Cadence 收购Secure-IC

Cadence今天宣布已达成最终协议,收购领先的嵌入式安全 IP 平台提供商 Secure-IC。Secure-IC 的人才和高度互补、经过验证的嵌入式安全 IP、安全解决方案、安全评估工具和服务组合将增强 Cadence 快速扩展的尖端、经过硅验证的 IP 产品组合,包括接口、内存、AI/ML 和 DSP 解决方案。 在我们日益互联的世界里,每个半导体、芯片和电子系统都需要嵌入式安全性。无

芯片设计

芯查查资讯 . 2025-01-23 5 1 2055

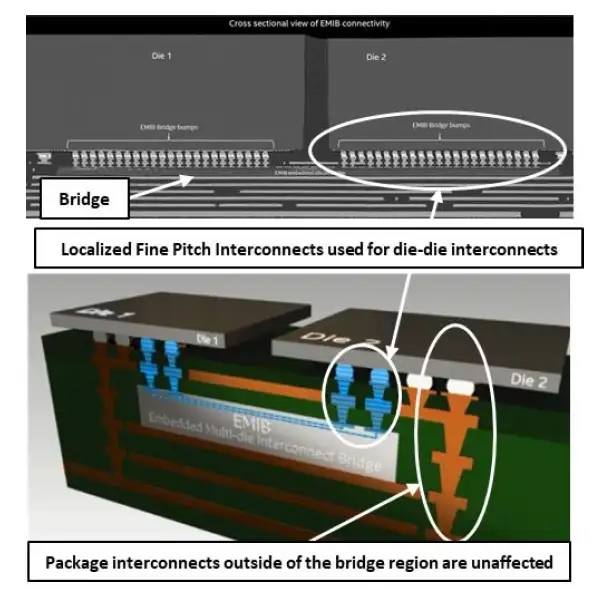

Cadence与Intel代工厂合作,通过EMIB封装技术实现异构集成

3月11日,Cadence发文称,Cadence与Intel代工厂合作开发并验证了一项集成的先进封装流程。该流程能利用嵌入式多晶粒互连桥接(EMIB)技术来应对异构集成多芯粒架构不断增长的复杂性。此次合作意味着Intel客户将能够利用先进封装技术来加速高性能计算(HPC)、人工智能和移动设备计算的设计空间方面的进步。这一先进的 EMIB 流程将使设计团队受益,帮助他们从早期系统级规划、优化和分析无

快讯

芯闻路1号 . 2024-03-11 2 2356

Cadence宣布以12.4亿美元收购BETA CAE Systems

3月6日消息,Cadence Design Systems近日表示,将以12.4亿美元的现金和股票(其中7.44亿美元为现金)收购BETA CAE Systems,后者生产用于分析汽车和喷气设计的软件。 Cadence 是最大的计算机芯片设计软件制造商之一,帮助芯片制造商设计复杂的集成电路。但在过去的六年里,它已经转向从电路板到飞机等大型物理系统的设计软件。上个月,该公司宣布推出一款超级计算机

快讯

芯闻路1号 . 2024-03-06 1 1 2891

Cadence 推出全新数字孪生平台 Millennium Platform

内容提要 ● 颠覆性的专用软硬件加速平台;利用 GPU 和 CPU 计算以及专有软件算法,提高准确度、速度和规模的同时,带来高达 100 倍的设计效率提升 ● 与传统 HPC 相比,支持 GPU-resident 模式的求解器可将仿真能效显著提高 20 倍 ● 将数字孪生、人工智能和 HPC 技术相结合,为汽车、航空航天、能源、叶轮机械和数据中心提供更优的多物理场仿真解决方案

快讯

Cadence楷登 . 2024-02-02 2810

Cadence 推出 Allegro X AI,旨在加速 PCB 设计流程,可将周转时间缩短 10 倍以上

“楷登电子今日宣布推出 Cadence® Allegro® X AI technology,这是 Cadence 新一代系统设计技术,在性能和自动化方面实现了革命性的提升。这款 AI 新产品依托于 Allegro X Design Platform 平台,可显著节省 PCB 设计时间,与手动设计电路板相比,在不牺牲甚至有可能提高质量的前提下,将布局布线(P&R)任务用时从数天缩短至几分钟。 ”

Cadence

Cadence . 2023-04-07 3003

Cadence 完成收购 Future Facilities

2022 年 7 月 22 日 —— 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布已完成对 Future Facilities 的收购。Future Facilities 的先进技术和专业能力将支持 Cadence® 智能系统设计(Intelligent System Design™)战略,助力 Cadence 进一步拓展其多物理场系统分析和计算流体力学(CFD)产品

Cadence

芯闻路1号 . 2022-07-24 2217

高塔半导体宣布与 Cadence 合作开发汽车和移动 IC 芯片

7 月 14 日,Tower Semiconductor 公司宣布与 Cadence 合作推动汽车和移动 IC 开发。 通过合作,两家公司正在开发一种新的、全面的汽车参考设计流程,使用 Cadence Virtuoso 设计平台和 Spectre 仿真平台,为客户提供更快的设计周期,为先进的汽车 IC 产品开发保持全面的设计验证。 Tower Semiconductor 的首席执行官

高塔半导体

芯闻路1号 . 2022-07-17 2614

模拟IC升级需要什么样的EDA工具支持?

IC设计离不开EDA工具的支持,模拟设计也不例外。在9月20日举行的2019年中国模拟半导体大会上,Cadence中国区技术支持总监栾志雨带来了主题为《中国模拟IC升级更需要借力EDA工具》的演讲,在本次演讲中,他阐述了针对16nm及以下节点工艺的模拟IC设计需要注意的问题。 图1:Cadence中国区技术支持总监栾志雨。 流程规范化 目前大家普遍都认为数字芯片的设计流程更加规范和自动化,不过这几

模拟IC

电子发烧友 . 2019-09-25 1745

Cadence宣布新的Tensilica Vision P6 DSP瞄准嵌入式神经网络应用

与上一代Vision DSP相比,最新的DSP四倍神经网络性能 加利福尼亚州圣何塞, 2016年5月2日/PRNewswire/--Cadence Design Systems,Inc。(纳斯达克股票代码:CDNS)今天宣布推出全新Cadence®Tensilica®VisionP6数字信号处理器(DSP),这是Cadence的最高性能视觉/成像处理器,将Tensilica产品组合进一步扩展到快速

Cadence

LONG . 2019-08-07 3615

Cadence发布Cadence Sigrity 2018版本,可帮助设计团队进一步缩短PCB设计周期

美国Cadence公司近日宣布发布Cadence Sigrity 2018版本,该版本包含最新的3D解决方案,帮助PCB设计团队缩短设计周期的同时实现设计成本和性能的最优化。 独有的3D设计及分析环境,完美集成了Sigrity工具与CadenceAllegro技术,较之于当前市场上依赖于第三方建模工具的产品,Sigrity 2018版本可提供效率更高、出错率更低的解决方案,大幅度缩短设计周期的同

pcb

网络整理 . 2018-07-25 1210

DDR4已经OUT Cadence宣布DDR5全新进展

DDR4内存目前还是绝对主流,不断被深入挖潜,频率已经突破5GHz,不过下一代DDR5也已经蠢蠢欲动了。Cadence公司今天就宣布了DDR5的全新进展,无论工艺还是频率都相当领先。 目前,JEDEC标准组织正在研究下一代DDR5内存规范,已经有了初步版本,Cadence此番拿出的就是面向新规范的第一个DDR5 IP物理层接口芯片。 该测试芯片采用台积电7nm工艺制造,数据率可达4400MT/s,

Cadence

未知 . 2018-05-11 950

首款3nm测试芯片成功流片 采用极紫外光刻(EUV)技术

日前,纳米电子与数字技术研发创新中心 IMEC 与美国楷登电子( Cadence) 公司联合宣布,得益于双方的长期深入合作,业界首款 3nm 测试芯片成功流片。该项目采用极紫外光刻(EUV)技术,193 浸没式(193i)光刻技术设计规则,以及 Cadence® Innovus™ 设计实现系统和 Genus™ 综合解决方案,旨在实现更为先进的 3nm 芯片设计。IMEC 为测试芯片选择了业界通用的

Cadence

未知 . 2018-03-19 1330

2016:期盼IP发展能有更多新火花

商用IP已成为当今SoC设计公认的主流,很难想像若没有广大IP供应商生态系统所提供的高品质处理器、DSP、汇流排架构、DDR控制器、记忆体巨集、标准元件、I/O控制器、高速PHY与主要类比介面,大部份现今各大电子平台是否仍会存在。而2016年商用IP是否也将如同以往,各家供应商只期望在各方面推进一点就好?答案是对、也是不对。 我们应该都能预期全球电子创新周期的发展趋势——更高的产品密度、更多晶

Cadence

eettaiwan . 2016-02-05 1580

从Fabless到Chipless,芯片厂商怎么活

小编语:SoC的形式早已有之,只是近些年智能手机和物联网带动的应用全面智能化的大势让它从仅有半导体厂商关注的角落走到前台,有越来越多的设备、终端厂商也开始关注,其实这也代表着互联网思维的一个必然去处,即供应链被逐渐压缩,芯片厂商从只关心器件级开始考虑终端用户该干的事儿,终端厂商也反过来开始向上游倒推做起器件来了,而这种商业界线的打破背后的动因不过是为“逐利”,而已…… 物联网应用开枝散叶,带动

物联网

-- . 2015-08-13 2000

- 1