目录:

1.晶体是什么?

2.晶体的特性与等效电路

3.晶体的工作原理(驱动电路)

4.晶体的匹配电容计算过程

5.STM32晶体的选型(跨导计算)

6. 晶体不起振的常见原因与解决方案7.晶体设计、过程中的建议

1.晶体是什么?

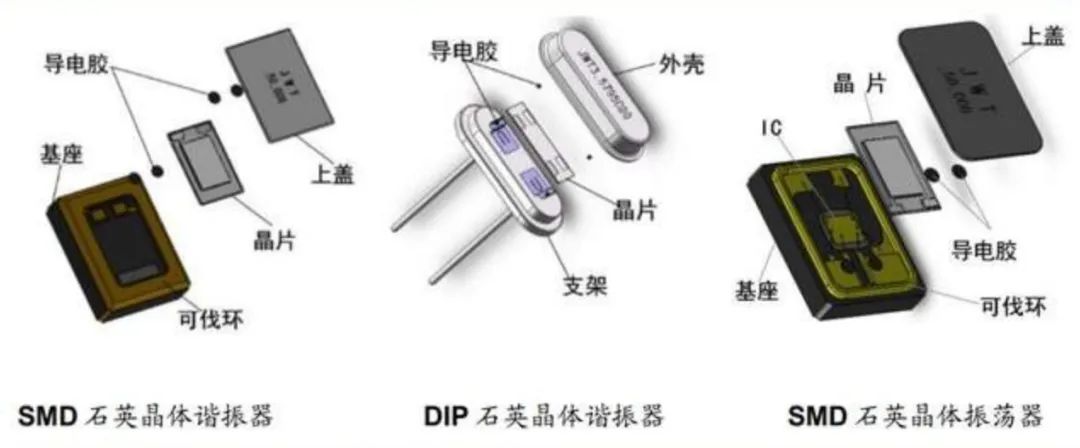

晶体是晶体谐振器的简称,谐振器是指 产生谐振频率的元器件 ,主要起频率控制的作用,广泛应用于各种电子。晶体谐振器封壳里面只有晶片,没有任何电路,参数有负载电容,频差,电阻。在焊接电路中,两旁需要电容电阻等电子元器件来助起振。

什么是晶振?

晶振是晶体振荡器的简称,也叫有源晶振。谐振器与振荡器的区别在于,在原有谐振器的基础上了加了起振芯片,封壳里带有电路 IC ,参数有电压值 输出模式 控制脚等参数。简而言之在焊接电路上的体现为,无需在外部添加其它的元器件,自身就可以起振,有源晶振通常的用法:一脚悬空,二脚接地,三脚接输出,四脚接电压。

晶振的作用在于产生原始的时钟频率,这个频率经过频率发生器的倍频或分频后就成了电脑中各种不同的总线频率。

晶体的最重要的几个参数:标称频率(Normal Frequency):晶振的标准频率,如 26MHz、32.768KHz 等。

频率误差(Frequency Tolerance)或频率稳定度(Frequency Stability):用单位 ppm 来表示,即百万分之一,是相对标称频率的变化量,此值越小表示精度越高,1MHz 的晶振,1 个 PPM 就是 1Hz 的偏差。

温度频差(Frequency Stability vs Temp):表示在特定温度范围内,工作频率相对于基准温度时工作频率的允许偏离,它的单位也是 ppm。

负载电容 CL:负载电容是指晶振正常工作震荡所需要的电容。为使晶体能够正常工作,需要在晶体两端外接电容,来匹配达到晶体的负载电容。

2.晶体的特性与等效电路

1880年,居里兄弟Jacques和Pierre Curie发现了石英晶体受到压力时,表面会产生电荷,电荷量和外机械力成正比的关系。这种现象为压电效应Piezoelectricity。具有压电效应的物体称为压电体。如果对石英晶片施加压力,晶片上会产生电荷;反之,对晶片两端的电极施加电压时,晶体会产生机械变形。

将石英晶片按一定的形状进行切割后,再用两个电极板夹住就形成了无源晶振,其符号图如下所示:

下图是一个在谐振频率附近有与晶体谐振器具有相同阻抗特性的简化电路。

其中:C1为动态等效串联电容;

L1为动态等效串联电感;

R1为动态等效串联电阻,它是晶体内部摩擦性当量

C0为静态电容,相当于两个电极板之间的电容量;

这个等效电路有如下图所示的频响特性曲线:

当R1、L1、C1串联支路发生谐振的频率即串联谐振频率(Fr),此时容抗与感抗相互抵消,因此,支路相当于只有等效串联电阻R1。

这个频率是晶体的自然谐振频率,它在高稳晶振的设计中,是作为使晶振稳定工作于标称频率、确定频率调整范围、设置频率微调装置等要求时的设计参数(但不是标称频率),其表达式如下所示:

等效串联电阻R1决定晶体元件的品质因数,品质因数又称机械Q值,它是反映谐振器性能好坏的重要参数,它与L1和C1有如下关系:

R1越大,Q值越低,会导致频率不稳定,反之,Q值越高,频率越稳定,晶体的特点在于它具有很高的品质因素。

等效电路还有一个反谐振频率fL(并联谐振频率),此时串联支路呈现为感抗,相当于一个电感,如下图所示:

此时的频率如下图所示:

通常厂家的晶振元件数据手册给出的标称频率不是Fr或FL,实际的晶体元件应用于振荡电路中时,它一般还会与负载电容相联接,共同作用 使晶体工作于Fr和FL之间的某个频率 ,这个频率由振荡电路的相位和有效电抗确定,通过改变电路的电抗条件,就可以在有限的范围内调节晶体频率。

(1)当负载电容与晶体串联时, 如下图所示:

串接的小电容CL可以使石英晶体的谐振频率在一个小范围内调整,此时新的负载谐振频率如下式所示:

其中,C1远远小于C0+CL

(2)当负载电容与晶体并联时,如下图所示:

同样,并联的负载CL也可以小范围调整谐振频率,相应的负载谐振频率如下式:

从实际效果上看,对于给定的负载电容值,F’r与F’L两个频率是相同的,这个频率是晶体的绝大多数应用时所表现的实际频率,也是制造厂商为满足用户对产品符合标称频率要求的测试指标参数,也就是本文最开头介绍的晶振标称频率。

3.晶体的工作原理(驱动电路)

晶体是晶体谐振器的简称,谐振器是指 产生谐振频率的元器件 ,主要起频率控制的作用,广泛应用于各种电子。晶体谐振器封壳里面只有晶片,没有任何电路,参数有负载电容,频差,电阻。在焊接电路中,两旁需要电容电阻等电子元器件来助起振。

无源晶体本身不能产生振荡信号,需要加外部振荡电路,分为串联型振荡电路和并联型振荡电路两种。

(1)串联晶体振荡器是一种反馈性振荡器,由放大器和反馈网络组成。石英谐振器和负载电容串联。谐振器为纯阻性 。

(2)并联晶体振荡器石英谐振器接在反馈支路中,工作在串联和并联谐振频率之间,谐振器为感性。在电路中作为电感元件使用。电路匹配电容C1, C2加上电路的杂散电容Cstray,越接近晶体的负载电容,晶体输出的频率则越精准。

一般单片机都会有这样的电路。晶振的两个引脚与芯片(如单片机)内部的反相器相连接,再结合外部的匹配电容CL1、CL2、R1、R2,组成一个皮尔斯振荡器(Pierce oscillator)。

U1: 增益很大的反相放大器。

X1: 晶体。相当于电容三点式电路里面的电感。

CL1、CL2: 匹配电容。是电容三点式电路的分压电容,接地点就是分压点。以接地点即分压点为参考点,输入和输出是反相的,但从并联谐振回路即石英晶体两端来看,形成一个正反馈以保证电路持续振荡,它们会稍微影响振荡频率,主要用与微调频率和波形,并影响幅度。

R1: 反馈电阻(一般≥1MΩ)它使反相器在振荡初始时处于线性工作区。

R2: 限流电阻,与匹配电容组成网络,提供180度相移,同时起到限制振荡幅度,防止反向器输出对晶振过驱动将其损坏。

皮尔斯振荡器电路的理论分析比较复杂,有兴趣可以自己仿真一下:

4.晶体的匹配电容计算过程

负载电容CL(Load capacitance),是电路中跨接晶体两端的总的有效电容(不是晶振外接的匹配电容),主要影响负载谐振频率和等效负载谐振电阻,与晶体一起决定振荡器电路的工作频率,通过调整负载电容,就可以将振荡器的工作频率微调到标称值。在一般情况下,增大负载电容会使振荡频率下降,而减小负载电容会使振荡频率升高。

一般 IC 的数据手册中会给出负载电容的大小。计算公式:CL=CL1*CL2/(CL1+CL2)+Cic+△CCL1 和 CL2 为晶振两脚对地电容,称为匹配电容。Cic 为集成电路内部电容(也就是规格书里面写的shunt capacitance)△C 为 PCB 板上电容,一般大小为 3~5pF。两个匹配电容的容值相等:CL 1 =CL2综上,可得匹配电容的容值为:CL1=CL2=2*(CL-Cic-△C)

匹配电容的容值确定之后:

选择NPO/COG高频材质的贴片陶瓷电容(外观看起来是白色的)。

尽量选择小封装的电容(封装小的器件寄生参数小)。

因为每一种晶振都有各自的特性,所以最好按制造厂商所提供的数值选择外部元器件。

在许可范围内,C1,C2值越低越好。C值偏大虽有利于振荡器的稳定,但将会增加起振时间。

5.STM32晶体的选型(跨导计算)

为了确保晶振能顺利起振,并运行在稳定状态,就得有足够的增益来维持。ST官方要求是:单片机的gm比晶振的gmcrit大5倍以上。

首先看STM32F103手册,可以直接获知:gm = 25mA/V

有了gm = 25mA/V,就要用它跟晶振的最小稳定跨导gmcrit相比较。

gmcrit的计算公式:

其中:

ESR——晶振的等效串联电阻

F——晶振的振荡频率

C0——晶振的Shunt Capacitance

CL——晶振的负载电容Load Capacitance

以上参数均可以从晶体规格书中找到:

F = 8MHz,C0 = 7pF,CL = 20pF,ESR = 80Ω。计算:

gmcrit = 4*80*(2Π*8*10^6)^2*(7*10^-12 + 20*10^-12)^2

gmcrit = 0.1886

现在gm、gmcrit都有了,可以比一下:

比值 = gm/gmcrit = 25/0.1886 = 132

可见,这个比值是132,远大于5倍的最低要求,所以我们选择的晶振是合适的。如果算出来是不合适的,那就要选用更小ESR,更低CL的晶振。其实STM32对于高速晶振的要求不高,但是对于外部低速RTC晶振的要求高一些,选型时要多加留意。

6.晶体不起振的常见原因与解决方案

晶振不起振问题归纳

1、物料参数选型错误导致晶振不起振

例如:某MCU需要匹配6PF的32.768KHz,结果选用12.5PF的,导致不起振。

解决办法:更换符合要求的规格型号。必要时请与MCU原厂确认。

2、内部水晶片破裂或损坏导致不起振

运输过程中损坏、或者使用过程中跌落、撞击等因素造成晶振内部水晶片损坏,从而导致晶振不起振。

解决办法:更换好的晶振。平时需要注意的是:运输过程中要用泡沫包厚一些,避免中途损坏;制程过程中避免跌落、重压、撞击等,一旦有以上情况发生禁止再使用。

3、振荡电路不匹配导致晶振不起振

影响振荡电路的三个指标:频率误差、负性阻抗、激励电平。

频率误差太大,导致实际频率偏移标称频率从而引起晶振不起振。

解决办法:选择合适的PPM值的产品。

负性阻抗过大太小都会导致晶振不起振。

解决办法:负性阻抗过大,可以将晶振外接电容Cd和Cg的值调大来降低负性阻抗;负性阻抗太小,则可以将晶振外接电容Cd和Cg的值调小来增大负性阻抗。一般而言,负性阻抗值应满足不少于晶振标称最大阻抗3-5倍。

激励电平过大或者过小也将会导致晶振不起振

解决办法:通过调整电路中的Rd的大小来调节振荡电路对晶振输出的激励电平。一般而言,激励电平越小越好,处理功耗低之外,还跟振荡电路的稳定性和晶振的使用寿命有关。

4、晶振内部水晶片上附有杂质或者尘埃等也会导致晶振不起振

晶振的制程之一是水晶片镀电极,即在水晶片上镀上一次层金或者银电极,这要求在万级无尘车间作业完成。如果空气中的尘埃颗粒附在电极上,或者有金渣银渣残留在电极上,则也会导致晶振不起振。

解决办法:更换新的晶振。在选择晶振供应商的时候需要对厂商的设备、车间环境、工艺及制程能力予以考量,这关系到产品的品质问题。

5、晶振出现漏气导致不起振

晶振在制程过程中要求将内部抽真空后充满氮气,如果出现压封不良,导致晶振气密性不好出现漏气;或者晶振在焊接过程中因为剪脚等过程中产品的机械应力导致晶振出现气密性不良;均会导致晶振出现不起振的现象。

解决办法:更换好的晶振。在制程和焊接过程中一定要规范作业,避免误操作导致产品损坏。

6、焊接时温度过高或时间过长,导致晶振内部电性能指标出现异常而引起晶振不起振

以32.768KHz直插型为例,要求使用178°C熔点的焊锡,晶振内部的温度超过150°C,会引起晶振特性的恶化或者不起振。焊接引脚时,280°C下5秒以内或者260°C以下10秒以内。不要在引脚的根部直接焊接,这样也会导致晶振特性的恶化或者不起振。

解决办法:焊接制程过程中一定要规范操作,对焊接时间和温度的设定要符合晶振的要求。

7、储存环境不当导致晶振电性能恶化而引起不起振

在高温或者低温或者高湿度等条件下长时间使用或者保存,会引起晶振的电性能恶化,可能导致不起振。

解决办法:尽可能在常温常湿的条件下使用、保存,避免晶振或者电路板受潮。

8、MCU质量问题、软件问题等导致晶振不起振

解决办法:目前市场上面MCU散新货、翻新货、拆机货、贴牌货等鱼龙混杂,如果没有一定的行业经验或者选择正规的供货商,则极易买到非正品。这样电路容易出现问题,导致振荡电路不能工作。另外即便是正品MCU,如果烧录程序出现问题,也可能导致晶振不能起振。

9、EMC问题导致晶振不起振

解决办法:一般而言,金属封装的制品在抗电磁干扰上优于陶瓷封装制品,如果电路上EMC较大,则尽量选用金属封装制品。另外晶振下面不要走信号线,避免带来干扰。

7.晶体设计、过程中的建议

1、在PCB布线时,晶振电路的走线尽可能的短直,并尽可能靠近MCU。尽量降低振荡电路中的杂散电容对晶振的影响。

2、PCB布线的时候,尽量不要在晶振下面走信号线,避免对晶振产生电磁干扰,从而导致振荡电路不稳定。

3、如果你的PCB板比较大,晶振尽量不要设计在中间,尽量靠边一些。这是因为晶振设计在中间位置会因PCB板变形产生的机械张力而受影响,可能出现不良。

4、如果你的PCB板比较小,那么建议晶振设计位置尽量往中间靠,不要设计在边沿位置。这是因为PCB板小,一般SMT过回流焊都是多拼板,在分板的时候产生的机械张力会对晶振有影响,可能产生不良。

5、在选择晶振的型号及规格参数时,工程师应尽量与晶振大厂商或者专业代理商确认,避免选择的尺寸或者指标不常用,导致供货渠道少、批量供货周期长而影响生产,而且在价格上也会处于被动。

6、通常不建议用超声波清洗带有晶体振荡器的电路板,以避免共振对晶振造成损坏。

参考文献:

- https://blog.csdn.net/tutuforu/article/details/84935471

- https://caifuhao.eastmoney.com/news/20220527113019448218420

- https://www.sohu.com/a/253591227_208903

- https://www.sohu.com/a/458084766_120774276

- javascript:void(0)

- javascript:void(0)

- javascript:void(0)

- https://blog.csdn.net/Seaman_TY/article/details/93090532https://zhuanlan.zhihu.com/p/540062435

点击此处报名EPSON直播:如何精确匹配晶体电路?| 12月26日14:30

全部评论