(本文编译自trendforce网站)

台积电业务发展高级副总裁Kevin Zhang在2024年国际固态电路会议(ISSCC)上介绍了公司的最新技术。据TechNews援引演讲稿报道,Kevin Zhang分享了对未来技术进步、先进工艺前景以及各个领域所需的最新半导体技术的见解。

Kevin Zhang指出,自ChatGPT和Wi-Fi 7推出以来,进入半导体未来的加速增长期,需要大量先进的半导体。

在汽车行业,该行业正在经历一场革命,许多人认为新车将是软件定义的中心,Zhang认为,这更多的是关于硅定义的,因为软件需要在硅上运行,从而推动自动驾驶能力的未来。

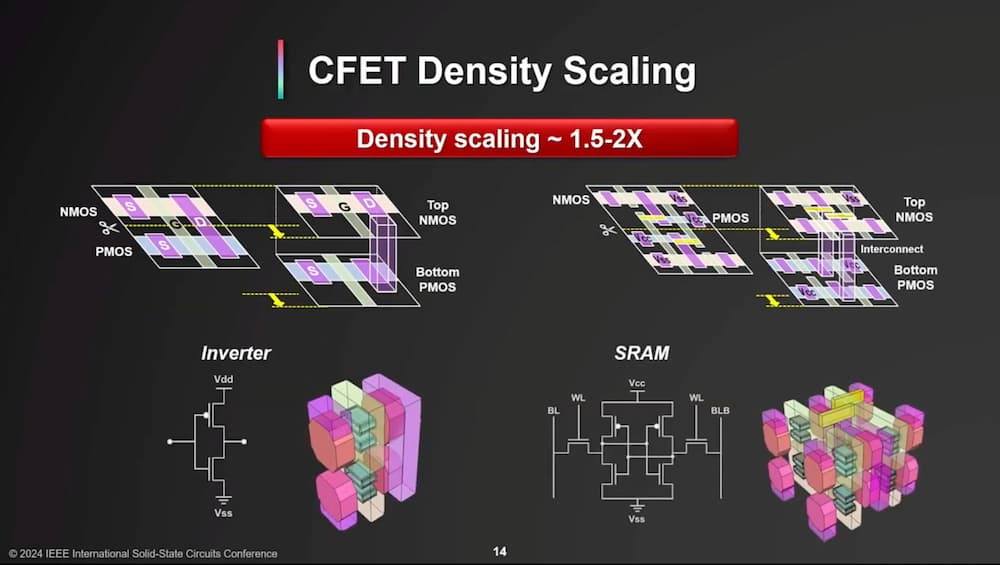

CFET(互补场效应晶体管)

在技术方面,晶体管仍然是创新的核心——硅创新,它已经从几何形状的减少转向建筑创新和新材料的使用。从 16 纳米 FinFET 到今天的 2 纳米纳米片技术,代表了高性能计算和架构创新的重大进步。

下一步是什么?答案是CFET。

Kevin Zhang解释说,CFET涉及将nMOS和pMOS堆叠在一起,从而显着改善组件电流并将晶体管密度提高1.5至2倍。

另外,人们正在努力用低维材料(如2D材料)制造更高性能的开关器件以超越当今的晶体管。

Kevin Zhang还展示了台积电在实验室中成功制造了CFET架构,他说:“这是我们实验室制造的真正集成设备。在这里你可以看到晶体管IV曲线,它们是美丽的曲线。因此,就继续推动晶体管架构创新而言,这是一个重要的里程碑。”

然而,晶体管几何形状的缩小,它变得越来越困难和昂贵,这需要工艺开发团队和设计研究之间的协作,以实现最佳效益,即“设计-技术协同优化”(DTCO)。

此外,台积电还引入了FINFLEX技术,使芯片设计人员能够选择和混合最佳的鳍片结构来支持每个关键功能块,从而实现最佳性能、密度和功耗。

DTCO的另一个例子是静态随机存取存储器(SRAM)。SRAM已从130纳米扩展到目前的3纳米,台积电实现了超过100倍的密度改进,这是合作或结合工艺创新和采用更先进的设计技术的结果。

然而,正如Kevin Zhang所表达的那样,这种技术扩展的本质或目标是“节能计算”。他表示,在整个半导体行业,台积电已经走了很长一段路,这一进步使今天的人工智能成为可能。

HPC/AI 技术平台的进步:3D 堆叠、硅光子学、CPO

无论是 GPU、TPU 还是定制的 ASIC,都具有这种特定的集成方案。目前主流的是2.5D封装。然而,为了满足未来的高性能计算需求,该平台需要显著增强,需要更高的密度和更低的功耗计算。

因此,需要堆叠,包括将许多内存带宽和 HBM 集成到封装中,同时考虑电源、I/O 和互连密度等问题。

因此,Kevin Zhang表示,将“硅光子学带入封装”是未来的方向,然而,这将面临许多挑战,例如更接近电子侧的共封装光学器件 (CPO)。

1. 3D堆叠

当谈到 3D 堆叠时,Kevin Zhang 展示了一张图表,并解释说,为了实现更高的互连密度,特别是芯片到芯片连接,3D 堆叠允许键合间距扩展到几微米,从而实现像单片一样的互连密度。“这就是为什么3D(堆叠)是未来,”他总结道。

2. 硅光子学/共封装光学器件 (CPO)

Kevin Zhang指出,虽然电子学擅长计算,但光子更适合信号或通信。他举例说,如果使用50 TB的交换机,全电子铜系统,它将消耗2,400 W。

目前的解决方案涉及使用可插拔模块,可以节省 40% 的功率(> 1500W)。然而,随着未来对更高速信号和更大带宽的需求增加,该解决方案已达不到要求。因此,集成硅光子学技术对于引入光子能力是必要的。

汽车技术

1. 追求低DPPM

从根本上说,最新的汽车技术需要大量的计算能力,但功耗正成为一个问题,特别是对于电池供电的汽车。

Kevin Zhang表示,由于严格的安全要求,汽车半导体技术已经落后于消费电子或HPC技术几代。汽车应用的 DPPM(每百万次缺陷数)必须接近于零。

因此,晶圆厂、半导体制造商和汽车设计人员必须更紧密地合作,以加快这一步伐。他还承诺,“不久之后,你就会在你的车里看到3纳米。

2. MRAM/RRAM

随着汽车向域架构过渡,MCU(微控制器单元)变得越来越重要,需要先进的半导体技术来提供计算能力。

传统的MCU主要依靠浮栅技术,但该技术在28纳米以下遇到瓶颈。幸运的是,业界已经投资了新的存储器技术,包括新的非易失性存储器,如磁性随机存取存储器(MRAM)或电阻式随机存取存储器(RRAM)。

因此,从MCU过渡到基于MRAM或RRAM的技术有助于推动技术从28纳米到16纳米甚至7纳米的持续扩展。

传感器和显示器:CIS(CMOS图像传感器)

传感器技术已经从简单的 2D 设计和单层设计发展到具有 3D 晶圆堆叠的智能系统,本质上是将信号处理分层在传感层之上。

Kevin Zhang还提到,“我们的技术已经开始投资,研究多层设计。

采用三层或更多层设计可以优化像素,延续像素尺寸缩放的趋势,同时满足分辨率要求并同时实现最佳传感能力。

另一个例子是AR(增强现实)和VR(虚拟现实),其中分离内存层并将它们堆叠到其他逻辑芯片上可以有效地减小尺寸,同时保持高性能需求。

全部评论